New technologies are often quite complex and optimized for specific specialized applications, and their applicability to multipurpose computing platforms is often limited. This article first summarizes the general power-saving techniques, then introduces some higher-payoff technologies (CPU clock idle and voltage and frequency scaling), and describes how these support technologies integrate into an auxiliary power manager module. Become a digital signal processor (DSP) real-time operating system. Here is an audio application example that shows how to use the architecture to significantly increase power efficiency. This article is the first in a series of articles devoted to low-power design. The second article will focus on peripherals and I/O power management techniques to extend power savings beyond the CPU core.

Power Saving Technology

The total power consumption of CMOS circuits is the sum of active power consumption and static power consumption. The active power consumption is generated when the circuit is switched from one logic state to another logic state; static power loss occurs when the circuit is not converted, which is mainly caused by transistor leakage current. The approximate equation for calculating the active power consumption is as follows:

Pactive ~ Cpd x F x Vcc2 x Nsw

Here Cpd is a dynamic capacitor, F is the switching frequency, Vcc is the supply voltage, and Nsw is the number of bits converted. From the equation above, the easiest way to save on active power consumption is to stop the circuit timing, that is, set F to zero and let Pactive be zero. Many CPUs have "idle" or "stop" instructions for this purpose, which gate the internal CPU clock off when the CPU waits for an interrupt. In addition, some processors include discrete controls that gate off non-CPU clock domains such as caches, DMAs, peripherals, clock pulse generators, and so on.

Looking back at the equation above, if the application can still meet the processing requirements while reducing the CPU clock rate, then the active power consumption can be proportionally saved accordingly. If the CPU frequency can be safely reduced and this frequency is compatible with the lower operating voltages available to the CPU, then due to the quadratic relationship of Vcc, the power consumption can be significantly reduced by reducing the voltage. However, reducing the CPU clock rate also prolongs the task execution time proportionally, which requires careful analysis of the application to see if it can still meet real-time requirements.

Add power management support for the OS

Clock idleness and dynamic frequency and voltage scaling can have a huge impact on overall applications and the operating system itself, which is often an obstacle to implementing the above techniques. For example, if the CPU frequency scaling is dynamic, it may affect the OS time base, and The peripheral driver that caused the clock to be associated with the CPU clock is faulty. Similarly, if a task is arbitrarily leaving the CPU idle while waiting for I/O to complete, it can easily cause the application to deadlock. Therefore, in order to actively adopt the above technologies, the OS power consumption must be power aware, and certain operational responsibilities (such as idle CPU clock) must be borne by the OS.

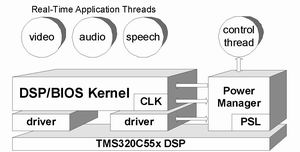

Texas Instruments' DSP/BIOS operating system adds a Power Manager Module (PWRM) as an auxiliary module, as shown in Figure 1. The power manager is loosely coupled to the OS kernel and is located next to the kernel; it does not exist as another task in the system, but exists as a set of APIs that execute under application control threads and device driver environments.

Figure 1 Power Manager partition

Through the above APIs, the power manager can support voltage and frequency (V/F) scaling, frequency scaling only, clock domain idle, automatic idle configuration of the clock during OS idle time, and most importantly, power consumption events in the entire application. Coordination between processes (such as application code, drivers, and the OS itself) is used to notify when registered client-specific power events occur. Examples of power usage events are: the frequency to be scaled, the completion of the scaling frequency, entering a deep sleep state, waking from a deep sleep state, lack of power, and the like. The power management activities are triggered applications; the main decision to change the DSP operating mode or function is made by the application and helps by calling the power manager.

PWRM is directly connected to the DSP hardware by writing to the clock idle configuration registers and the platform-specific power conditioning library (PSL) that controls the CPU clock rate and voltage regulator circuitry. The PSL isolates the PWRM and other parts of the application from the low-level implementation details of the frequency and voltage control hardware to ensure a safe transition between the supported voltage and frequency combinations (setpoints).

Audio example

Use a simple audio application as a vehicle and use it as a benchmark for testing the efficiency of power manager features. This application is modified to measure the effect of activating different power saving features. The current sensing resistor board power supply and the DSP core power supply are connected in series, and the voltage drop across the resistor is measured with a voltmeter to determine the current of the motherboard and the DSP core.

Concluding remarks

Adopting a phased approach to implementing power management can greatly reduce power consumption. It is not necessary to wait for the results of the new technology research currently underway to achieve results; in some cases, combining the basic and practical key supporting technologies into the operating system or application framework can achieve CPU power savings of more than 95%. Power management support can be designed in such a way that it is easy to use, allows developers to select specific technologies that meet specific application requirements, and is very portable. The framework can serve as a springboard to prepare for the addition of new and more advanced specialized technologies and future power management technologies

Nantong Boxin Electronic Technology Co., Ltd. , https://www.bosencontrols.com