When designing a digital circuit, everyone knows that synchronization is very important, especially when you want to input a signal into a synchronous circuit, but when the signal is driven by another clock, this is to take some measures at the interface to make the input asynchronous signal. Synchronization, otherwise the circuit will not work properly, because the input is likely to have metastability, resulting in sampling errors.

Below we will introduce some of the principles, causes, hazards, solutions, effects on reliability and elimination of simulations of metastable states.

2. What is metastable?Metastability means that the trigger cannot reach an identifiable state within a specified period of time. When a flip-flop enters a metastable state, it is impossible to predict the output level of the cell or predict when the output will stabilize at a certain level. During this stabilization period, the flip-flop outputs some intermediate level, or may be in an oscillating state, and this useless output level can propagate along the various flip-flops on the signal path.

3. Causes of metastabilityIn a synchronous system, if the trigger's setup time / hold time is not satisfied, a metastable state may occur. At this time, the flip-flop output Q is in an indeterminate state for a long period of time after the valid clock edge. The Q-end glitch, oscillation, and fixed voltage value at the time is not equal to the value of the data input terminal D. This period becomes the resolution time. After the resolution time, the Q terminal will stabilize to 0 or 1, but whether it is 0 or 1, this is random and has no necessary relationship with the input.

4. Metastable hazardsSince the output may be a glitch, oscillation, or fixed voltage value before it stabilizes, in addition to causing a logical misjudgment, the intermediate voltage between 0 and 1 will cause the next stage to metastable. State (ie, causing the propagation of metastability). Logical misjudgment may be mitigated by the special design of the circuit (such as the role of the Gray code counter in the asynchronous FIFO), while the propagation of the metastable state expands the fault surface and is difficult to handle.

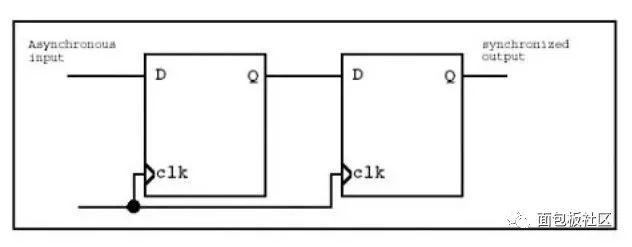

5. Metastable solutionAs long as there are asynchronous components in the system, metastability is unavoidable, so the circuit is designed to reduce the occurrence of errors by metastability first, and secondly to make the system insensitive to errors. The former should be implemented synchronously, while the latter has different treatments depending on the design application. A typical circuit that uses synchronization to reduce the chance of metastability is shown in Figure 1.

Figure 1 two-stage synchronization circuit

In Figure 1, the left side is the asynchronous input. After two levels of flip-flop synchronization, the output on the right will be synchronous, and the output is essentially free of metastability. The principle is that even if the output of the first flip-flop has a metastable state, after a CLK cycle, the probability that the level of the D-side of the second flip-flop is still not stable is very small, so the Q-end of the second flip-flop is basically not Will produce metastable state. Note that what is said here is "basic", that is, it cannot be "eradicated". So what happens if the second trigger Q has a metastable state?

The severity of the consequences is determined by your design. If the system is not sensitive to the errors generated, the system may work normally, or it can resume normal operation after a short exception. For example, when designing an asynchronous FIFO, use the Gray code counter to read and write. The pointer to the address is considered in this regard. If the design does not consider how to reduce the sensitivity of the system to metastability, then once metastability occurs, the system may collapse.

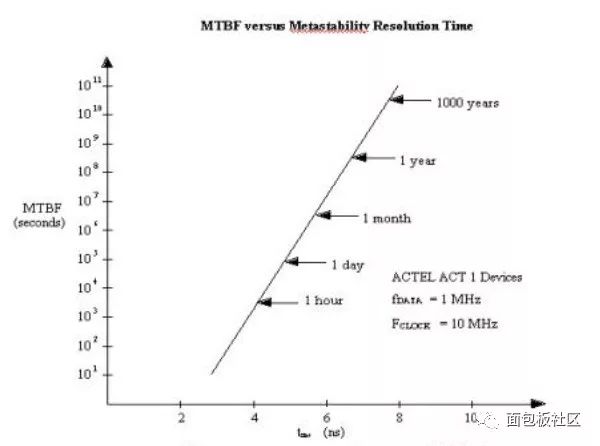

6. Metastable and system feasibilityAfter using the synchronous circuit, the metastable state still occurs. The connection is related to MTBF (Mean Time Between Failure). The probability of occurrence of metastability is independent of the clock frequency, but the MTBF is closely related to the clock. An article provides an example. When a system is operating at a 20MHz clock, the MTBF is about 50 years, but when the clock frequency is increased to 40MHz, the MTBF is only 1 minute! It can be seen that reducing the clock frequency can greatly reduce the occurrence of system errors caused by metastability. The reason is that providing a longer resolution time can reduce the chance of metastable transmission to the next stage and improve the MTBF of the system, as shown in Figure 2. Show.

Figure 2 Relationship between resolution time and MTBF

Metastable state has a very close relationship with design reliability. Currently, for many designs, it is not difficult to achieve the required functions. It is difficult to improve the stability and reliability of the system, and the probability of occurrence of a small metastable state. Reducing the system's sensitivity to metastability errors can increase system reliability.

Powerwall Battery is a high-tech product developed to meet the requirements of the new home backup power supply. It has the characteristics of integration, miniaturization, light weight, intelligence, standardization, and environmental protection.ZTTEK-48V-100Ah has a lithium (LiFePO4) battery storage capacity of 5kWh, allowing you to stay away from the grid as you like.

Home Solar Energy Storage,Home Solar Energy Storage Battery,Home Energie Storage Batterie,Lithium Battery For Solar Energy Storage

Jiangsu Zhitai New Energy Technology Co.,Ltd , https://www.zt-tek.com